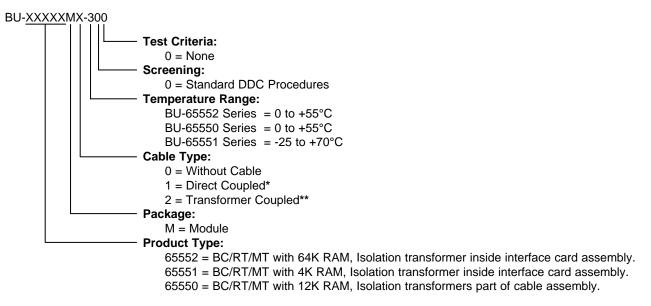

# BU-65552, BU-65551 and BU-65550

# MIL-STD-1553 BC/RT/MT INTERFACE CARD

# DESCRIPTION

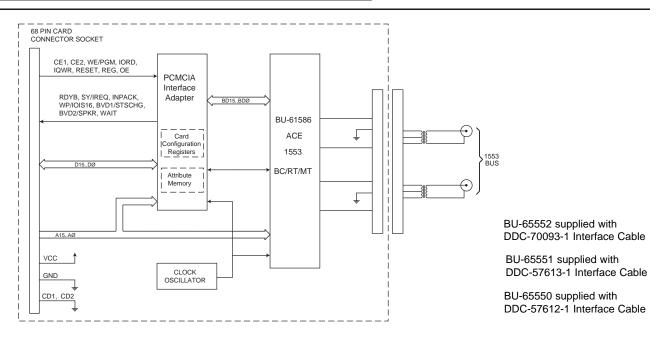

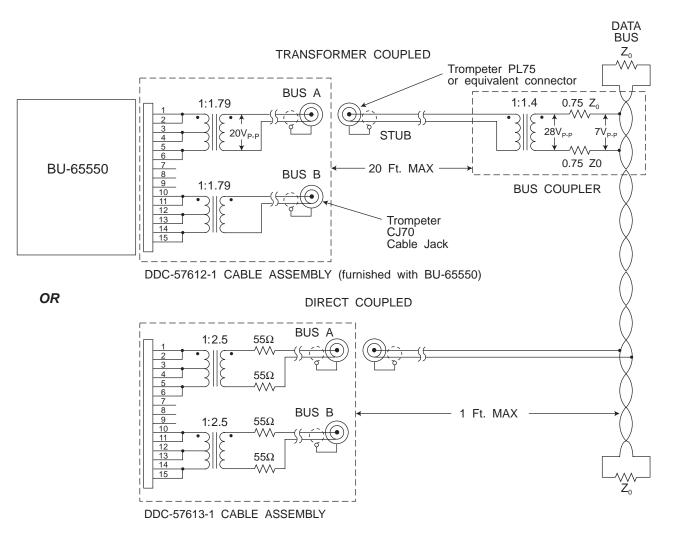

The BU-65552, BU-65551 and BU-65550 provide full, intelligent interfacing between a dual redundant MIL-STD-1553 Data Bus and a PCM-CIA socket. Software controls these cards operation as either a 1553 Bus Controller (BC). Remote Terminal (RT), or Bus Monitor (MT). The BU-65552, BU-65551 and BU-65550 are packaged in a Type II PCMCIA PC Card. The BU-65552 is designed around the Mini-ACE Plus, which has backward compatability to the BU-61586 and provides 64k x 16 onboard shared RAM. Using the supplied drivers and libraries, this card will require only 32k bytes of PC memory. The The BU-65552, BU-65551 and BU-65550 feature DDC's BU-61586 Advanced Communication Engine (ACE). As such, it includes dual transceiver and encoder/decoder, complete 1553 protocol, shared RAM and memory management logic for all three modes. On-board Interrupt Mask and Interrupt Status Registers support flexible operation for both interrupt

and polling applications. The memory management scheme for RT mode provides an option for separation of broadcast data plus a circular buffer option for individual RT subaddresses to offload the host CPU. The PCMCIA interface includes 256 bytes of attribute memory as well as the four standard PCMCIA card configuration registers. Additional features include a wrap-around Built-In-Test, and software programmable RT address selection. Free C Runtime Library and comprehensive Menu Applications for DOS, Windows 95/98 and Windows NT. These cards support all dual redundant mode codes and message formats. Additionally, these cards allow the use of commercial off-theshelf or ruggedized laptop and notebook computers in applications requiring a MIL-STD-1553 interface. Full compliance with both MIL-STD-1553 and PCMCIA 2.10 make the BU-65552, BU-65551 and BU-65550 an excellent choice for real-time simulation, test, and system integration applications.

# FEATURES

- Type II PCMCIA 2.10 Compatible PC Card

- MIL-STD-1553 Dual Redundant BC\RT\MT with Simultaneous RT/Monitor

- Multiprotocol Support of MIL-STD-1553A and B Notice 2

- Flexible RT Data Buffering

- Selective Message Monitor

- 64K x 16 Shared RAM (BU-65552)

- 4K x 16 Shared RAM (BU-65551)

- 12K x 16 Shared RAM (BU-65550)

- Runtime Libraries for Windows 3.1, Windows 95/98 and Windows NT

- Menu Software for Windows 3.1, Windows 95/98 and Windows NT

#### FIGURE 1. BU-65552, BU-65551 AND BU-65550 BLOCK DIAGRAM

| TABLE 1. BU-65552, BU-65551 AND BU-65550 SPECIFICATIONS                                                                                                         |                                                                                                                                          |                                    |                              |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------|--------------------------------------|

| PARAMETER                                                                                                                                                       | MIN                                                                                                                                      | TYP                                | MAX                          | UNITS                                |

| ABSOLUTE MAXIMUM RATINGS<br>+5 V Supply Voltage                                                                                                                 | -0.3                                                                                                                                     |                                    | 7.0                          | V                                    |

| RECEIVER<br>Threshold Voltage, Transformer<br>Coupled, Measured on Stub                                                                                         | 0.200                                                                                                                                    |                                    | 0.860                        | Vp-p                                 |

| Common Mode Voltage                                                                                                                                             |                                                                                                                                          |                                    | 10                           | Vреак                                |

| TRANSMITTER<br>Differential Output Voltage<br>■ Direct Coupled Across 35 ohms,<br>Measured on Bus                                                               | 6                                                                                                                                        | 7                                  | 9                            | Vp-p                                 |

| <ul> <li>Transformer Coupled,<br/>Measured on Stub</li> </ul>                                                                                                   | 18                                                                                                                                       | 20                                 | 27                           | Vp-p                                 |

| Output Noise, Differential<br>(Direct Coupled)                                                                                                                  |                                                                                                                                          |                                    | 10                           | mVр-р,<br>diff                       |

| Output Offset Voltage,<br>Direct Coupled Across 35 ohms                                                                                                         | -90                                                                                                                                      |                                    | 90                           | mV                                   |

| Rise/Fall Time                                                                                                                                                  | 100                                                                                                                                      |                                    | 300                          | nsec                                 |

| POWER SUPPLY REQUIREMENTS<br>Voltages/Tolerances<br>■ + 5 V<br>Current Drain @ + 5.0 V                                                                          | 4.5                                                                                                                                      |                                    | 5.5                          | v                                    |

| <ul> <li>Idle</li> <li>25% Transmitter Duty Cycle</li> <li>50% Duty Cycle</li> <li>100% Duty Cycle</li> </ul>                                                   |                                                                                                                                          | 80<br>225<br>385<br>700            | 110<br>300<br>490<br>860     | mA<br>mA<br>mA<br>mA                 |

| POWER DISSIPATION<br>Total PC Card (Vcc = +5.0 V)<br>Idle<br>25% Duty Cycle<br>50% Duty Cycle<br>100% Duty Cycle                                                |                                                                                                                                          | 0.4<br>0.98<br>1.16<br>1.47        | 0.55<br>1.18<br>1.81<br>3.07 | W<br>W<br>W<br>W                     |

| 1553 MESSAGE TIMING<br>RT Response Time<br>Completion of CPU Write<br>(BC Start-to Start of FIRST BC                                                            | 4                                                                                                                                        | 2.5                                | 7                            | μsec<br>μsec                         |

| Message)<br>BC Intermessage Gap<br>(See Note 1)<br>BC/RT/MT Response Timeout                                                                                    |                                                                                                                                          | 9.5                                |                              | μsec                                 |

| <ul> <li>(See Note 2)</li> <li>18.5 nominal</li> <li>22.5 nominal</li> <li>50.5 nominal</li> <li>128.0 nominal</li> <li>Transmitter Watchdog Timeout</li> </ul> | 17.5<br>21.5<br>49.5<br>127                                                                                                              | 18.5<br>22.5<br>50.5<br>128<br>668 | 19.5<br>23.5<br>51.5<br>129  | μsec<br>μsec<br>μsec<br>μsec<br>μsec |

| THERMAL<br>BU-65552<br>Operating Temperature<br>Storage Temperature<br>BU-65551                                                                                 | 0<br>-20                                                                                                                                 |                                    | 55<br>65                     | ပံ့                                  |

| Operating Temperature<br>Storage Temperature<br>BU-65550                                                                                                        | -25<br>-55                                                                                                                               |                                    | 70<br>80                     | ℃<br>℃                               |

| Operating Temperature<br>Storage Temperature<br>Vibration                                                                                                       | 0<br>-20                                                                                                                                 | - بىللەر مەر                       | 55<br>65                     | °C<br>°C                             |

| Shock<br>Operating Humidity<br>Non-operating Humidity                                                                                                           | Random vibration, 0.1 g <sup>2</sup> / Hz<br>from 20 Hz to 2000 Hz<br>40g, 11ms, half sine<br>0 to 95% non-condensing<br>100% condensing |                                    |                              | ) Hz<br>ine<br>nsing                 |

| TABLE 1. | BU-65552,   | BU-65551 | AND | BU-6 | 5550 S | PECIFIC | ATIONS |

|----------|-------------|----------|-----|------|--------|---------|--------|

| (continu | (continued) |          |     |      |        |         |        |

|          |             |          |     |      | î      | 1       |        |

| PARAMETER                | MIN                   | TYP      | MAX    | UNITS |

|--------------------------|-----------------------|----------|--------|-------|

| PHYSICAL CHARACTERISTICS |                       |          |        |       |

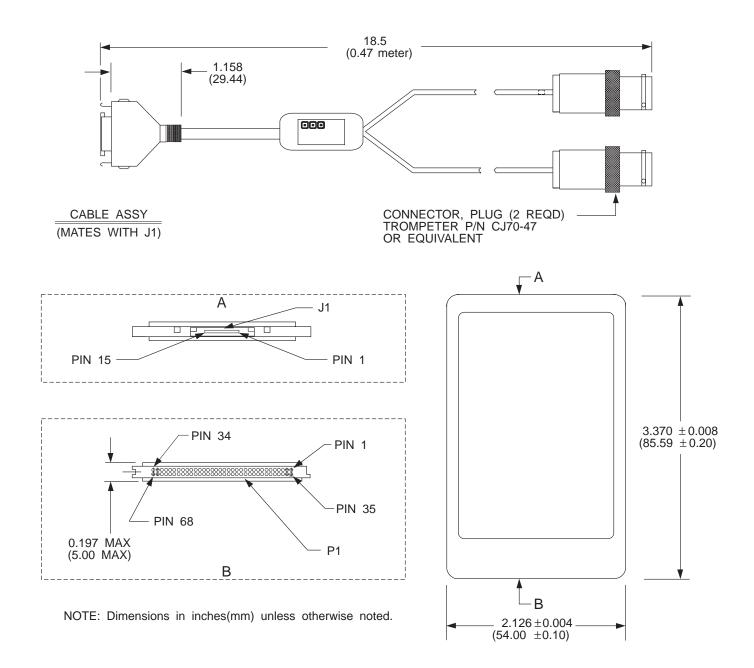

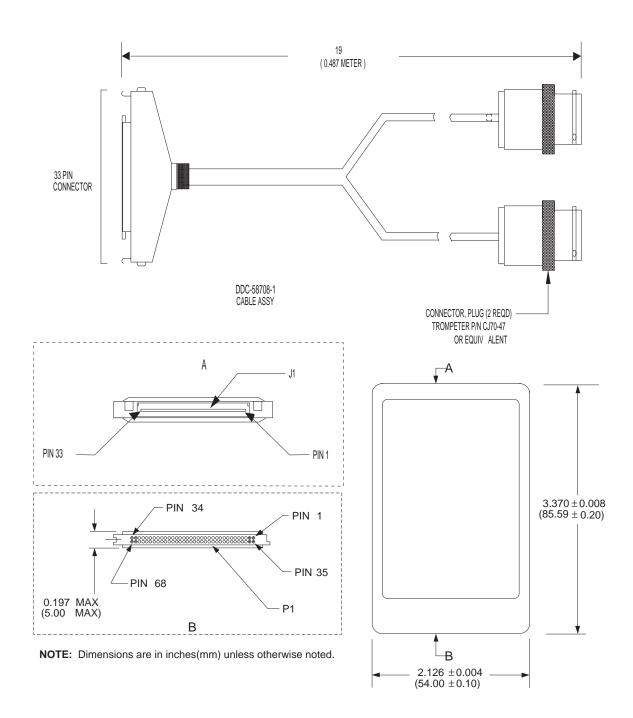

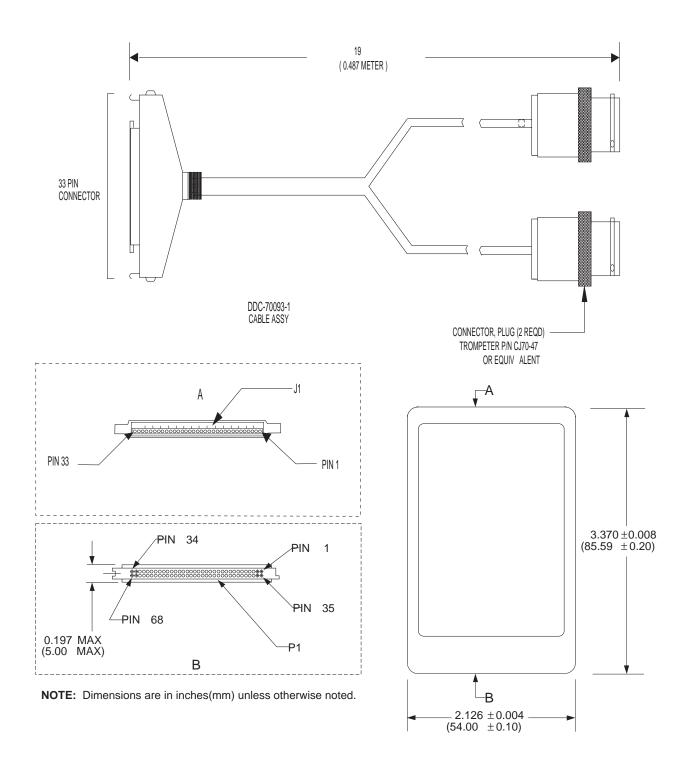

| Size                     | 3.370 x 2.126 x 0.197 |          |        | in    |

|                          | (85.6                 | x 54.0 x | x 5.0) | (mm)  |

| Weight                   |                       | 2.8      |        | oz    |

| _                        |                       | (80)     |        | (gm)  |

#### Notes:

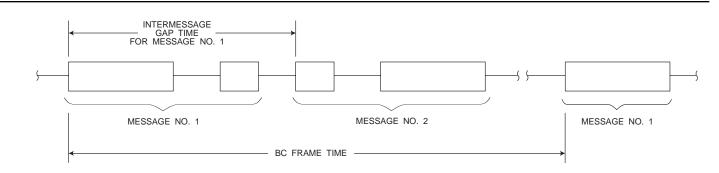

(1) Typical value for minimum intermessage gap time. Under software control, may be lengthened to (65,535 ms minus message time), in increments of 1  $\mu$ s. (2) Software programmable (4 options). Includes RT-to-RT Timeout (Mid-Parity of Transmit Command to Mid-Sync of Transmitting RT Status).

| TABLE 2. HOST SYSTEM REQUIREMENTS                               |

|-----------------------------------------------------------------|

| HARDWARE REQUIREMENTS                                           |

| Socket Interface Compliant with PCMCIA Release 2.10 or higher   |

| SOFTWARE REQUIREMENTS                                           |

| Card Services Driver Compliant to PCMCIA Release 2.10 or higher |

# FUNCTIONAL OVERVIEW

#### GENERAL

The BU-65552, BU-65551 and BU-65550 (See FIGURE 1) provides a user-friendly interface between the serial MIL-STD-1553 Bus and a PCMCIA interface socket. The operating modes of these cards are controlled through the use of 24 on-board registers. 1553 message traffic is stored and retrieved using the dedicated, memory mapped, on-board 12K words of RAM. The various registers control and operate the BU-65552, BU-65551 and BU-65550. They include the five Configuration Registers, Start/Reset Register, Time Tag Register, Interrupt Mask Register, and Interrupt Status Register. The Configuration Registers define the operating mode and memory management features. The Start/Reset Register provides various reset and BC/MT start functions. The Interrupt Mask Register enables desired interrupts, with the interrupt priority level being jumper programmable by the user. The cause of interrupts may be determined by a single READ operation, by means of the Interrupt Status Register. The Time Tag Register features programmable resolution and is used to time tag messages in BC, RT, or MT modes.

The BU-65552 64K x16 of static RAM is shared by the PC host and the 1553 Bus with memory arbitration handled automatically by the BU-65552.

The BU-65551 4K x16 of static RAM is shared by the PC host and the 1553 Bus with memory arbitration handled automatically by the BU-65551.

The BU-65550 12K x16 of static RAM is shared by the PC host and the 1553 Bus with memory arbitration handled automatically by the BU-65550.

The BU-65552, BU-65551 and BU-65550 will withhold the WAIT signal (assert to logic "0") to the PCMCIA socket interface while a word is being transferred to or from the 1553 Bus. Since the memory arbitration is handled by simply stretching the hand-shake cycle, the wait state is transparent to the PC host processor's software. A maximum wait of 2.6  $\mu$ s can occur

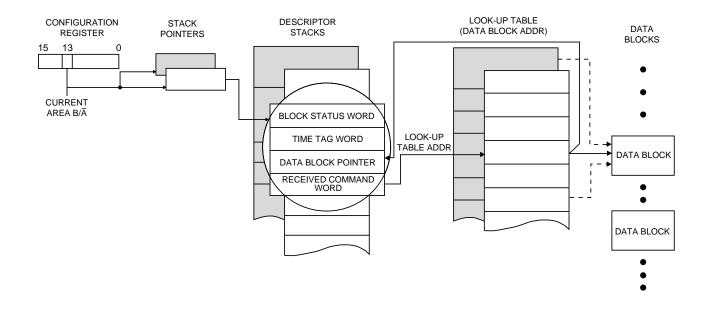

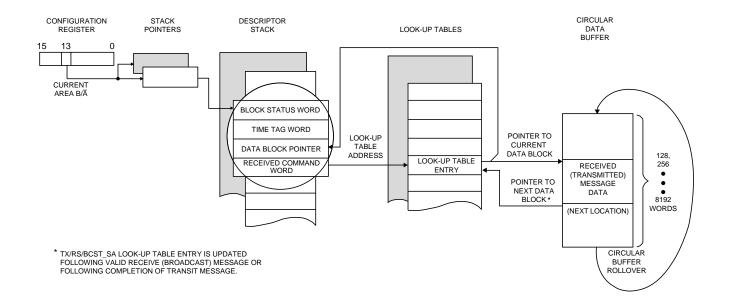

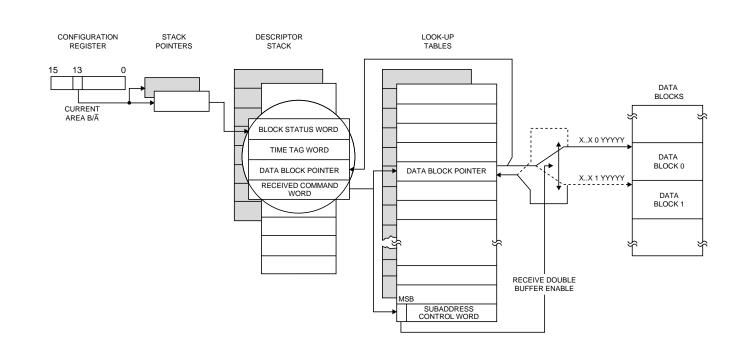

In addition to storing the 1553 message data, the RAM implements the Stacks and Look-Up Tables required for the different modes of operation. A global double buffering mechanism is available to prevent partially updated information from being transferred to or from the 1553 Bus. For RT mode, there is a programmable option to separate broadcast message data from non-broadcast data. This provides compliance to MIL-STD-1553. In addition, for RT mode, there is the choice of storing either a single message, a double buffer data structure, or a circular buffer data structure. The size of the circular buffer is programmable up to 8192 words, on a Tx/Rx/Bcst-subaddress basis.

The BU-65552, BU-65551 and BU-65550 support programmable command illegalization for RT mode. This allows individual Command Words to be illegalized as a function of  $T/\overline{R}$  bit, sub-address, and word count/mode code. Since the illegalization scheme is RAM based, it is inherently self-testable.

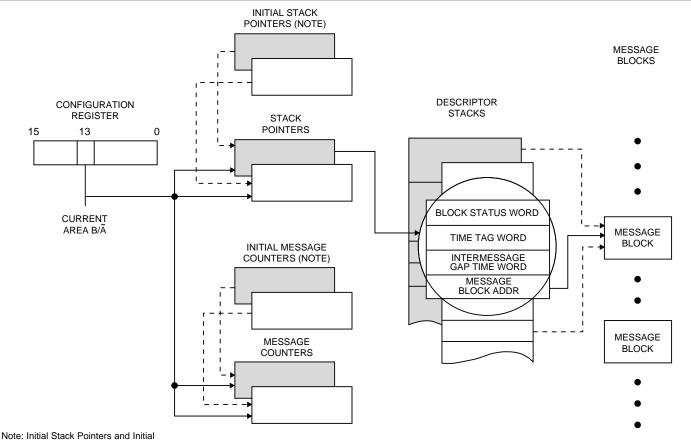

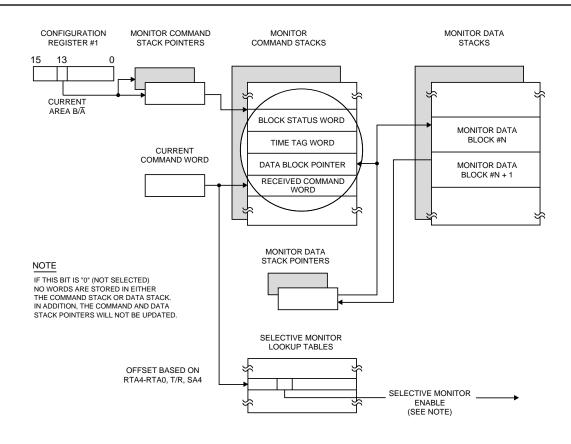

A Descriptor Stack or Command Stack is maintained for BC, RT, and MT modes. This records the status of each message, the time the message was transmitted or received, and contains either the received 1553 command and Data Block Pointer (in RT or MT mode) or the actual address of the 1553 message block (in BC mode). In RT mode, a Lookup Table is provided to store the addresses of the data blocks to be used when receiving or transmitting messages for the individual subaddresses.

The PC Cards RT mode is multiprotocol, supporting MIL-STD-1553A, MIL-STD-1553B Notice 2, STANAG 3838 (including EFA bus), and the McAir A3818, A5232, and A5690 protocols.

The BU-65552, BU-65551 and BU-65550 implement three monitor modes: a word monitor, a selective message monitor, and a combined RT/selective message monitor.

#### **PCMCIA INTERFACE**

The BU-65552, BU-65551 and BU-65550 provide a Card Information Structure (CIS) within the attribute memory space of the PCMCIA interface. The CIS contains device configuration information structures called basic compatibility tuples. The format of these configuration tuples is defined within the PCMCIA interface standard. In addition to the CIS there are the four standard PCMCIA configuration registers (Configuration Option Register, Card Configuration and Status Register, Pin Replacement Register, and Socket and Copy Register).

The CIS, also referred to as the Metaformat, provides a level of device information which allows a card resource manager or an application program to identify and fully configure the card.

#### MEMORY MANAGEMENT

The BU-65552, BU-65551 and BU-65550 incorporate complete memory management and processor interface logic. The software interface to the host processor is implemented by means of 24 on-board registers plus up to 64K words of RAM. For all three modes, a stack area of RAM is maintained. In BC mode, the stack allows for the scheduling of multimessage frames. For all three modes, the stack provides a real-time chronology of all messages processed. In addition to the stack processing, the memory management logic performs storage, retrieval, and manipulation functions involving pointer and message data structures for all three modes.

The BU-65552, BU-65551 and BU-65550 provide a number of programm-able options for RT mode memory management. In compliance with MIL-STD-1553, received data from broadcast messages may be optionally separated from nonbroadcast received data. For each transmit, receive or broadcast subaddress, either a single-message data block or a variable-sized (128 to 8192 words) circular buffer may be allocated for data storage. In addition to helping ensure data consistency, the circular buffer feature provides a means of greatly reducing host processor overhead for bulk data transfer applications. End-of-message interrupts may be enabled either globally, following error messages, on a Tx/Rx/Bcst-subaddress basis, or when any particular Tx/Rx/Bcst-subaddress circular buffer reaches its lower boundary.

# INTERRUPTS

The BU-65552, BU-65551 and BU-65550 provide many programmable options for interrupt generation and handling. The interrupt output pin ( $\overline{\rm INT}$ ) has three software programmable modes of operation: a pulse, a level output cleared under software control, or a level output automatically cleared following a read of the Interrupt Status Register.

Individual interrupts are enabled by the Interrupt Mask Register. The host processor may easily determine the cause of the interrupt by using the Interrupt Status Register. The Interrupt Status Register provides the current state of the interrupt conditions. The Interrupt Status Register may be updated in two ways. In the standard interrupt handling mode, a particular bit in the Interrupt Status Register will be updated only if the condition exists and the corresponding bit in the Interrupt Mask Register is enabled. In the enhanced interrupt handling mode, a particular bit in the Interrupt Status Register will be updated if the condition exists regardless of the contents of the corresponding Interrupt Mask Register bit. In any case, the respective Interrupt Mask Register bit enables an interrupt for a particular condition.

The BU-65552, BU-65551 and BU-65550 provide maskable interrupts and 15-bit Interrupt Status Register for end of message, end of BC message list, erroneous messages, Status Set (BC mode), Time Tag Register Rollover, RT Address Parity Error conditions, BC retry, data stack rollover, command stack rollover, transmitter watchdog timeout, or RAM parity error. The Interrupt Status Register allows the host processor to determine the cause of all interrupts by means of a single READ operation.

# INTERNAL COMMAND ILLEGALIZATION

The BU-65552, BU-65551 and BU-65550 implemen internal command illegalization for RT mode. The illegalization architecture allows for any subset of the 4096 possible combinations of broadcast/own address,  $T/\bar{R}$  bit, subaddress, and word count/mode code to be illegalized. The illegalization scheme is under software control of the host processor. As a result, it is inherently self-testable.

#### INTERNAL TIME TAG

The BU-65552, BU-65551 and BU-65550 include an internal read/writable Time Tag Register. This register is a CPU read/writable 16-bit counter with a programmable resolution of either 2, 4, 8, 16, 32, or 64  $\mu$ s per LSB. Another option allows the Time Tag Register to be incremented under software control. This supports self-test for the Time Tag Register.

For each message processed, the value of the Time Tag register is loaded into the second location of the respective descriptor stack entry ("TIME TAG WORD") for both BC and RT modes.

Additional options are provided to clear the Time Tag Register following a Synchronize (without data) mode command or load the Time Tag Register following a Synchronize (with data) mode command. Another option enables an interrupt request and a bit in the Interrupt Status Register to be set when the Time Tag Register rolls over from FFFF to 0000 (hex). Assuming the Time Tag Register is not loaded or reset, this will occur at approximately 4-second time intervals, for 64  $\mu$ s/LSB resolution, down to 131 ms intervals, for 2  $\mu$ s/LSB resolution.

Another programmable option for RT mode is for the Service Request Status Word bit to be automatically cleared following the PC Cards response to a Transmit Vector Word mode command.

# ADDRESSING, INTERNAL REGISTERS, MEMORY MANAGEMENT, AND INTERRUPTS

# ADDRESSING THESE CARDS

All internal pointers used by these cards are assumed to be **word** addresses, however **byte** addressing is used by the PC to access memory and registers in the card. For example, to access the the Area A Stack Pointer at word offset address 0100 (hex), a byte address offset of 0200 (hex) must be used (i.e. the byte address is determined by multiplying the word address by two).

The shared RAM space starts at **byte** location 8000 if the memory allocation were contiguous. The registers are mapped into memory locations 0X0000 through 0X002F. The memory address space between 0X0030 and 0X7FFF is reserved. The 64K x 16 RAM uses page swapping, which is done in the device driver.

#### **COMMON MEMORY ADDRESS MAP**

The software interface of the BU-65552, BU-65551 and BU-65550 to the host processor consists of 17 internal operational registers for normal operation, an additional 8 test registers, plus shared memory (64K x 16 for BU-65552, 4K x 16 for BU-65551 and 12K x 16 for BU-65550). Both the registers and the shared memory reside in the PCMCIA common memory space. See TABLE 3. The BITMAPS of the 17 internal registers are shown in TABLES 4 through 21.

Definition of the address mapping and accessibility for the BU-65552, BU-65551 and BU-65550 17 nontest registers, and the test registers, is as follows:

| TABL                                                                                                                                               | TABLE 3. COMMON MEMORY ADDRESS MAPPING                              |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| HEX                                                                                                                                                | DESCRIPTION/ACCESSIBILITY                                           |  |  |  |  |

| ADDRESS                                                                                                                                            |                                                                     |  |  |  |  |

| 0000, 0001                                                                                                                                         | Interrupt Mask Register (RD/WR)                                     |  |  |  |  |

| 0002, 0003                                                                                                                                         | Configuration Register # 1 (RD/WR)                                  |  |  |  |  |

| 0004, 0005                                                                                                                                         | Configuration Register # 2 (RD/WR)                                  |  |  |  |  |

| 0004, 0005                                                                                                                                         | Configuration Register # 2 (RD/WR)                                  |  |  |  |  |

| 0006, 0007                                                                                                                                         | Start/Reset Register (WR)                                           |  |  |  |  |

| 0006, 0007                                                                                                                                         | BC/RT Command Stack Pointer Register (RD)                           |  |  |  |  |

| 0008, 0009                                                                                                                                         | BC Control Word/RT Subaddress Control Word<br>Register (RD/WR)      |  |  |  |  |

| 000A, 000B                                                                                                                                         | Time Tag Register (RD/WR)                                           |  |  |  |  |

| 000C, 000D                                                                                                                                         | Interrupt Status Register (RD)                                      |  |  |  |  |

| 000E, 000F                                                                                                                                         | Configuration Register #3                                           |  |  |  |  |

| 0010, 0011                                                                                                                                         | Configuration Register #4                                           |  |  |  |  |

| 0012, 0013                                                                                                                                         | Configuration Register #5                                           |  |  |  |  |

| 0014, 0015                                                                                                                                         | Data Stack Address Register (RD/WR)                                 |  |  |  |  |

| 0016, 0017                                                                                                                                         | BC Frame Time Remaining Register (RD)*                              |  |  |  |  |

| 0018, 0019                                                                                                                                         | BC Time Remaining to Next Message Register (RD)*                    |  |  |  |  |

| 001A,001B                                                                                                                                          | BC Frame Time*/RT Last Command/MT Trigger Word*<br>Register (RD/WR) |  |  |  |  |

| 001C, 001D                                                                                                                                         | RT Status Word Register (RD)                                        |  |  |  |  |

| 001E, 001F                                                                                                                                         | RT BIT Word Register (RD)                                           |  |  |  |  |

| 0020, 0021                                                                                                                                         | Test Mode Register 0                                                |  |  |  |  |

|                                                                                                                                                    |                                                                     |  |  |  |  |

| •                                                                                                                                                  | •                                                                   |  |  |  |  |

| 002E,002F                                                                                                                                          | Test Mode Register 7                                                |  |  |  |  |

| 0030, 0031                                                                                                                                         | reserved                                                            |  |  |  |  |

|                                                                                                                                                    |                                                                     |  |  |  |  |

| •                                                                                                                                                  | •                                                                   |  |  |  |  |

| 7FFE, 7FFF                                                                                                                                         | reserved                                                            |  |  |  |  |

| 8000, 8001                                                                                                                                         | 12K x 16 Shared RAM (RD/WR) See NOTE below.                         |  |  |  |  |

|                                                                                                                                                    |                                                                     |  |  |  |  |

| •                                                                                                                                                  | •                                                                   |  |  |  |  |

| DFFE, DFFF                                                                                                                                         | 12K x 16 Shared RAM (RD/WR)                                         |  |  |  |  |

| E000, E001                                                                                                                                         | reserved                                                            |  |  |  |  |

|                                                                                                                                                    | •                                                                   |  |  |  |  |

| •                                                                                                                                                  | •                                                                   |  |  |  |  |

| FFFE, FFFF                                                                                                                                         | reserved                                                            |  |  |  |  |

| <ul> <li>NOTES: 1. Normally RAM Addresses will be defined as an offset from the base address</li> <li>2. BU-65551 shared RAM is 4K x 16</li> </ul> |                                                                     |  |  |  |  |

**Interrupt Mask Register:** Used to enable and disable interrupt requests for various conditions.

**Configuration Registers #1 and #2:** Used to select the PC Cards mode of operation, and for software control of RT Status Word bits, Active Memory Area, BC Stop-on-Error, RT Memory Management mode selection, and control of the Time Tag operation.

**Start/Reset Register:** Used for "command" type functions, such as software reset, BC/MT Start, Interrupt Reset, Time Tag Reset, and Time Tag Register Test. The Start/Reset Register includes provisions for stopping the BC in its auto-repeat mode, either at the end of the current message or at the end of the current BC frame.

**BC/RT Command Stack Pointer Register:** Allows the host CPU to determine the pointer location for the current or most recent message when the PC Card is in BC or RT mode.

**BC Control Word/RT Subaddress Control Word Register:** In BC mode, allows host access to the current or most recent BC Control Word. The BC Control Word contains bits that select the active bus and message format, enable off-line self-test, masking of Status Word bits, enable retries and interrupts, and specify MIL-STD-1553A or -1553B error handling. In RT mode, this register allows host access to the current or most recent Subaddress Control Word. The Subaddress Control Word is used to select the memory management scheme and enable interrupts for the current message. The read/write accessibility can be used as an aid for testing the ACE.

**Time Tag Register:** Maintains the value of a real-time clock. The resolution of this register is programmable from among 2, 4, 8, 16, 32, and 64  $\mu$ s/LSB. The TAG\_CLK input signal also may cause an external oscillator to clock the Time Tag Register. Start-of-Message (SOM) and End-of-Message (EOM) sequences in BC, RT, and Message Monitor modes cause a write of the current value of the Time Tag Register to the stack area of RAM.

**Interrupt Status Register:** Mirrors the Interrupt Mask Register and contains a Master Interrupt bit. It allows the host processor to determine the cause of an interrupt request by means of a single READ operation.

**Configuration Registers #3, #4, and #5:** Used to enable many of the BU-65552, BU-65551 and BU-65550 advanced features. These include all the enhanced mode features; that is, all the functionality beyond that of the previous generation product, the BUS-65529 that makes use of the Advanced Integrated Mux Hybrid with Enhanced RT Features (AIM-HY'er). For all three modes, use of the Enhanced Mode enables the various read-only bits in Configuration Register #1.

For BC mode, the enhanced mode features include the expanded BC Control Word and BC Block Status Word, additional Stop-On-Error and Stop-On-Status Set functions, frame auto-repeat, programmable intermessage gap times, automatic retries, expanded Status Word Masking, and the capability to generate interrupts following the completion of any selected message.

For RT mode, the enhanced mode features include the expanded RT Block Status Word, the combined RT/Selective Message Monitor mode, internal wrapping of the "RTFAIL" output signal (from the J' chip)to the "RTFLAG" RT Status Word bit, the double buffering scheme for individual receive (broadcast) subaddresses, and the alternate (fully software programmable) RT Status Word.

For MT mode, use of the enhanced mode enables use of the Selective Message Monitor, the combined RT/Selective Monitor modes, and the monitor triggering capability.

**Data Stack Address Register:** Used to point to the current address location in shared RAM used for storing message words (second Command Words, Data Words, RT Status Words) in the Selective Word Monitor mode.

**Frame Time Remaining Register:** Provides a read only indication of the time remaining in the current BC frame. The resolution of this register is  $100 \ \mu$ s/LSB.

**Message Time Remaining Register:** Provides a read only indication of the time remaining before the start of the next message in a BC frame. The resolution of this register is 1  $\mu$ s/LSB.

BC Frame/RT Last Command/MT Trigger Word Register: In BC mode, it programs the BC frame time for use in the frame auto-repeat mode. The resolution of this register is  $100 \ \mu s/LSB$ , with a range of 6.55 seconds. In RT mode, this register stores the current (or most previous) 1553 Command Word processed by the ACE RT; in the Word Monitor mode, this register specifies a 16-bit Trigger (Command) Word. The Trigger Word may be used to start or stop the monitor, or to generate interrupts.

Status Word Register and BIT Word Registers: Provide readonly indications of the BU-65552, BU-65551 and BU-65550 RT Status and BIT Words.

**Test Mode Registers 0-7:** These registers may be used to facilitate built-in testing of the BU-65552, BU-65551 and BU-65550.

# ACE Software

The BU-65552/BU-65551/BU-65550 are supplied with software Runtime Libraries for DOS, Windows 3.1, Windows 95/98 and Windows NT, and Menu programs for Windows 3.1, Windows 95/98 and Windows NT. This software is provided with the card at no extra cost.

# ACE MENU OVERVIEW

The ACE Menu provides an interface for all ACE BC/RT/MT cards. For detailed information about the ACE Menu, please refer to the ACE Menu User's Guide.

| 😋 Ace 32-Bit Menu for Windows - Ace Setup Window-1                                                            |          |

|---------------------------------------------------------------------------------------------------------------|----------|

| <u>File View BC BT MT Test Window H</u> elp                                                                   |          |

| 🖹 🖻 🖬 📕 Ver 🤋 🧏 🎒 🖪 🥂 🏧 🔐                                                                                     |          |

| 👺 Ace Setup Window-1                                                                                          | - 🗆 🗵    |

| Ace Menu for Windows<br>New file, not currently saved<br>ACE Device #: 0<br>BC Info:<br>0 BC Messages defined | <u> </u> |

| No BC Frames defined<br>BC Run save file: BC.asf                                                              |          |

| RT Info:<br>RT Address setup 1<br>RT Run save file: RT.asf                                                    | <b>_</b> |

| For Help, press F1                                                                                            |          |

#### FIGURE 2. ACE SETUP WINDOW

Each of the operating modes, Bus Controller (BC), Remote Terminal (RT), and Monitor Terminal (MT) can be setup independently with all parameters being saved to an ACE setup file (\*.ace). The card is only capable of running in one mode at a time. Each mode has its own run screen.

The ACE Menu is provides the necessary functionality for creating messages and assembling the messages into a frame for use by the BC function. The parameters for each message, including the command word, data words, and Bus selection are modifiable from the ACE Menu . Setup screens are available for setting other operational parameters such as Response Timeout, Retries and Stop-On criteria. Adding these messages to a frame structure creates a BC frame. The ACE Menu allows a frame to be a composition of many minor frames, where each minor frame will represent the same amount of time, but is not restricted to the same number of messages. The minor frame time is operator programmable. The number of minor frames times the minor frame time represents the Major Frame time. Once the frame is complete, the BC Run screen can be used to control the processing of the BC Frame. This screen displays operational status and provides controls for setting the minor frame time, the number of frames to send, and communication stack setup. The Stack setup allows the user to set the name and size of the stack. The Stack file where the 1553 bus traffic will be stored, and may be viewed at a later time.

| Bus Controller Mo       | _                                  | 7              |

|-------------------------|------------------------------------|----------------|

| Status Stopped          | Minor Frame<br>Time (μS)           | <u>R</u> un    |

| Frame & Msg Info.       | Major Frames 0                     |                |

| # of Frames 1           | To Send 🔽 Forever                  |                |

| User Msgs 1             | Major Frame<br>Completed           |                |

| Message Cou             | nt Error Count                     |                |

| 0                       | 0                                  |                |

| Communication St        | ack                                |                |

| File Name BC.asf        |                                    |                |

| Status                  | File Total Msg's 0                 | OK,Save        |

| Tabl Data               |                                    |                |

| Total Bytes 0<br>Stored | Max. Bytes 1000000<br>Stored Limit | <u>C</u> ancel |

Communication information is saved in stack files (\*.asf). The run screens allow configuration of the stack file location and size. All run modes provide the stack view capability. After running the card, the generated stack file can be viewed by opening the stack viewer. Within each of the operating mode tool bars and menus, there is an open stack button that allows quick access to the stack file open dialog. Once opened, the stack file can be searched for any type of message or error. These stack files are compatible with the previous version stack files for both the Windows 95 and Windows 3.xx ACE Menu programs.

The Remote Terminal mode operation allows setting the hardware to respond to a specified RT address. The setup for a RT is much simpler than that of a BC. The bulk of the setup is used to specify the data that should be returned based on the sub-address set in the message command word. The data edit screen provides controls to select the sub-address and enter the data. Once all of the sub-address responses have been determined, the operation of the RT is controlled in the Setup screen. The controls available here are the RT Address, Remote Terminal to Remote Terminal timeout, and status word bits set. Finally, the RT Run screen will provide options for setting the Remote Terminal Address, and the Stack File.

| RT Run Dialog                                                                                | ×                   |

|----------------------------------------------------------------------------------------------|---------------------|

| Remote Term inal Mode       Status     Stopped       Total Msg's     0       Monitored     0 | <u>B</u> un<br>Stop |

| Tx Count Rx Count                                                                            |                     |

| Communication Stack                                                                          |                     |

| File Name RT.asf                                                                             |                     |

| Status Total Msg's 0                                                                         | OK,Save             |

| Total Bytes 0 Max. Bytes 1000000 Stored                                                      | Cancel              |

#### FIGURE 4. RT RUN DIALOG WINDOW

Monitor operation is also provided. The ACE Menu monitor is a full message monitor that will monitor the 1553 bus traffic, decode the messages (command and data) and save the information to a Stack File. The monitor is capable of filtering the message information based on Remote Terminal address, Sub-address, and Transmit/Receive for each message. When all of the appropriate filtering has been established, the Response Timeout option may be set. The timeout option instructs the Monitor as to how long it must wait before declaring a no response message. The Run Monitor screen has controls that allow setting the Stack File requirements, and to provide access to the Monitor Trigger capabilities. The monitor is capable of triggering its capture based on any combination of the command word bits, or based on any of the error bits in the RT Status Word.

| Monitor Run Dialog                                                    | ×                                                                                   |

|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Monitor Mode                                                          | Communication Stack                                                                 |

| Monitor Stopped                                                       | Waiting on Monitor                                                                  |

| Time Elapsed (sec.) 0 Reset                                           | File: Mon.asf                                                                       |

| Total Commands Invalid Commands 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 | Save to File     250 Max Size (KB)       Msgs Stored     0       Bytes Stored     0 |

|                                                                       | Trigger 00 00                                                                       |

FIGURE 5. MONITOR MODE WINDOW

Finally, a Stack View capability is provided for each of the modes (BC, RT, and MT). From the Stack Button, a stack file can be selected, and viewed on the screen. Once the stack file is displayed, there is a capability of 'Finding' any message that was captured. The stack file contains information pertaining to the Storage Date, time and number of messages. It also contains the data portion of the messages, all pertinent status information, and text describing the error type.

| 🎯 Ace 3          | 32-Bit Men                | u for Windows - [Mon.asf]     |                            |           |                          | X |

|------------------|---------------------------|-------------------------------|----------------------------|-----------|--------------------------|---|

| 📁 <u>F</u> ile   | <u>E</u> dit <u>V</u> iew | v <u>W</u> indow <u>H</u> elp |                            |           | _ 8                      | × |

| 12               | <b>1</b>                  | er 🤋 🕺 🎒 🙆 🌢                  | • →目                       |           |                          |   |

| File:            | Mon.as                    | f 05/10/99 03:13PM            |                            | Total Mes | sages: 07523             |   |

| Msg:             | 1                         | Type: RT to BC<br>Cmd1: 0C22  | Time: 3330µS<br>01-T-01-02 | BSW: 9200 | CHANNEL A<br>No response |   |

| I                | Data:                     |                               |                            |           |                          |   |

| Msg:             |                           | Type: BC to RT<br>Cmd1: 0842  | Time: 3616µS<br>01-R-02-02 | BSW: 9300 | CHANNEL A<br>No response |   |

|                  | Data:                     | 0000 0000                     |                            |           |                          |   |

| Msg:             | 3                         | Type: RT to BC<br>Cmd1: 0C22  | Time: 5884µS<br>01-T-01-02 | BSW: 9200 | CHANNEL A<br>No response |   |

|                  | Data:                     | 5Ha11 5022                    | 01 1 01 02                 |           |                          | - |

| ,<br>For Help, j | press F1                  |                               |                            |           | NUM                      |   |

FIGURE 6. MONITOR MODE - STACK VIEW

The stack file can be searched by message command word, any data word, or any MIL-STD-1553 error. Each of the search criteria may be combined with a mask to allow searching for a family of command or data words. The search direction is selectable between up and down.

# ACE RUNTIME LIBRARIES

The Runtime Libraries come in both 16-bit and 32-bit versions to support 16 and 32 bit DOS and Windows. Using the Runtime Library, applications may be created that are capable of controlling the PCMCIA card in either the BC, RT or MT mode. The newest version of this Runtime Library supports C and Visual Basic programming. Included with the ACE Runtime Library are sample applications for Bus Controller, Remote Terminal, and Monitor mode control. There are also sample programs for self-test and loop back tests. The self-test program tests and reports any errors found with the major portions of the hardware including registers, RAM, interrupt generation, and the protocol unit. The loop back tests force the BU-65552|BU-65551|BU-65550 card to communicate with itself. This test verifies the protocol unit and the transceivers to a greater degree than is performed by the Selftst2 program. The source for all of the test and sample programs is provided free of charge. These source programs may be used as a starting point for custom applications.

The following source code represents the simplicity of writing code for the BU-6555X PCMCIA cards. This program sends 10 words of data to RT 1 sub-address 5 on channel A, followed by a 32 word transmit to RT 6 sub-address 1 on channel 'A'. It then receives 5

words from RT 8 sub-address 4 on channel 'A', followed by a 32 word receive from RT 7 sub-address 2 on channel 'A'. Note that the creation of a 32 word message requires only that the data be defined in a buffer, and then a single function call to BuSendData(...) be made. Similarly, to receive data from a RT, a buffer must be defined, and a call to BuGetData(...) will be made. This encapsulated functionality relieves the application developer from having to know the dirty details of the 1553 protocol hardware and registers.

The following code is from the BCDEMO1.C sample program supplied with the BU-6555X hardware.

```

#include <stdio.h>

#include <stdlib.h>

#include <stdace.h>

void main ()

ł

BuConf_t Conf; /* ACE library configuration type */

BuError_t Err; /* ACE library error status type */

U16BIT data[32]={ 0X0000,0x1111,0x2222,0x3333,0x4444,0x5555,0x6666,0x7777,

0x8888, 0x9999, 0xAAAA, 0xBBBB, 0xCCCC, 0xDDDD, 0xEEEE, 0xFFFF,

0x0001,0x0002,0x0004,0x0008,0x0010,0x0020,0x0040,0x0080,

0x0100,0x0200,0x0400,0x0800,0x1000,0x2000,0x4000,0x8000};

/* display revision info */

printf("%s\n\n",BuRev());

printf("\nThis BC Demo sets the Ace card in BC mode and sends a few messages.\n\n");

/* setup configuration for device X and open ACE library */

printf("Choose the logical device # of your BC:> ");

scanf("%d",&Conf.ConfDev);

Err=BuOpen32(&Conf);

if(Err) {

printf("BuError %d %s\n",Err,BuErrorStr(Err));

return;

}

/* opens bus controller mode */

BuBCOpen();

/* send 10 words to rt 5 sa 1 on channel A */

Err=BuBCSendData(CW_CHANNELA,5,1,data,10);

printf("%s\n",BuErrorStr(Err));

/* send 32 words to rt 6 sa 1 on channel A

added this [01-SEP-1995] to test 32 word case */

Err=BuBCSendData(CW_CHANNELA,6,1,data,32);

printf("%s\n",BuErrorStr(Err));

/* receive 5 words from rt 8 sa 4 on channel A */

Err=BuBCGetData(CW_CHANNELA,8,4,data,5);

printf("%s\n",BuErrorStr(Err));

/* display data */

if(!Err){int x;for(x=0;x<5;x++)printf("%04x ",data[x]);printf("\n");}

/* receive 32 words from rt 7 sa 2 on channel A

added this [01-SEP-1995] to test 32 word case */

Err=BuBCGetData(CW_CHANNELA,7,2,data,32);

printf("%s\n",BuErrorStr(Err));

/* display data */

if(!Err){int x;for(x=0;x<32;x++)printf("%04x ",data[x]);}

/* closes bus controller mode */

BuBCClose();

/* must call at end of ACE library use */

BuClose();

}

```

| TABLE 4. | TABLE 4. INTERRUPT MASK REGISTER (READ/WRITE 00H) |  |  |  |  |

|----------|---------------------------------------------------|--|--|--|--|

| BIT      | DESCRIPTION                                       |  |  |  |  |

| 15 (MSB) | RESERVED                                          |  |  |  |  |

| 14       | RAM PARITY ERROR                                  |  |  |  |  |

| 13       | TRANSMITTER TIMEOUT                               |  |  |  |  |

| 12       | BC/RT COMMAND STACK ROLLOVER                      |  |  |  |  |

| 11       | MT COMMAND STACK ROLLOVER                         |  |  |  |  |

| 10       | MT DATA STACK ROLLOVER                            |  |  |  |  |

| 9        | RT MODE CODE/MT PATTERN TRIGGER                   |  |  |  |  |

| 8        | BC RETRY                                          |  |  |  |  |

| 7        | RT ADDRESS PARITY ERROR                           |  |  |  |  |

| 6        | TIME TAG ROLLOVER                                 |  |  |  |  |

| 5        | RT CIRCULAR BUFFER ROLLOVER                       |  |  |  |  |

| 4        | RT SUBADDRESS CONTROL WORD EOM                    |  |  |  |  |

| 3        | BC END OF FRAME                                   |  |  |  |  |

| 2        | FORMAT ERROR                                      |  |  |  |  |

| 1        | STATUS SET                                        |  |  |  |  |

| 0 (LSB)  | END OF MESSAGE                                    |  |  |  |  |

|          | TABLE 5. CONFIGURATION REGISTER #1 (READ/WRITE 02H) |                                                           |                                             |                                                       |  |  |

|----------|-----------------------------------------------------|-----------------------------------------------------------|---------------------------------------------|-------------------------------------------------------|--|--|

| BIT      | BC FUNCTION<br>( Enhanced Mode Only<br>Bits 11-0)   | RT WITHOUT ALTERNATE<br>STATUS                            | RT WITH ALTERNATE<br>STATUS (Enhanced Only) | MONITOR FUNCTION<br>(Enhanced mode only<br>bits 12-0) |  |  |

| 15 (MSB) | RT/BC-MT (logic 0)                                  | (logic 1)                                                 | (logic 1)                                   | (logic o)                                             |  |  |

| 14       | MT/BC-RT (logic 0)                                  | (logic 0)                                                 | (logic 0)                                   | (logic 1)                                             |  |  |

| 13       | CURRENT AREA B/A                                    | CURRENT AREA B/A                                          | CURRENT AREA B/Ā                            | CURRENT AREA B/A                                      |  |  |

| 12       | MESSAGE STOP-ON-ERROR                               | MESSAGE MONITOR<br>ENABLED<br>(MMT)                       | MESSAGE MONITOR<br>ENABLED (MMT)            | MESSAGE MONITOR<br>ENABLED<br>(MMT)                   |  |  |

| 11       | FRAME STOP-ON-ERROR                                 | DYNAMIC BUS CONTROL<br>ACCEPTANCE                         | S10                                         | TRIGGER ENABLED<br>WORD                               |  |  |

| 10       | STATUS SET STOP-ON-MESSAGE                          | BUSY                                                      | S09                                         | START-ON-TRIGGER                                      |  |  |

| 9        | STATUS SET STOP-ON-FRAME                            | SERVICE REQUEST                                           | S08                                         | STOP-ON-TRIGGER                                       |  |  |

| 8        | FRAME AUTO-REPEAT                                   | SUBSYSTEM FLAG                                            | S07                                         | NOT USED                                              |  |  |

| 7        | EXTERNAL TRIGGER ENABLED                            | RTFLAG (Enhanced Mode<br>Only)                            | S06                                         | EXTERNAL TRIGGER<br>ENABLED                           |  |  |

| 6        | INTERNAL TRIGGER ENABLED                            | NOT USED                                                  | S05                                         | NOT USED                                              |  |  |

| 5        | INTERMESSAGE GAP TIMER<br>ENABLED                   | NOT USED                                                  | S04                                         | NOT USED                                              |  |  |

| 4        | RETRY ENABLED                                       | NOT USED                                                  | S03                                         | NOT USED                                              |  |  |

| 3        | DOUBLED/SINGLE RETRY                                | NOT USED                                                  | S02                                         | NOT USED                                              |  |  |

| 2        | BC ENABLED                                          | NOT USED                                                  | S01                                         | MONITOR<br>ENABLED(Read Only)                         |  |  |

| 1        | BC FRAME IN PROGRESS (Read Only)                    | NOT USED                                                  | S00                                         | MONITOR TRIGGERED<br>(Read Only)                      |  |  |

| 0 (LSB)  | BC MESSAGE IN PROGRESS<br>(Read Only)               | RT MESSAGE IN PROGRESS<br>(Enhanced mode only, Read Only) | RT MESSAGE IN PROGRESS<br>(Read Only)       | MONITOR ACTIVE<br>(Read Only)                         |  |  |

| TABLE 6. CONFIGURATION REGISTER #2 (READ/WRITE 04H) |                                |

|-----------------------------------------------------|--------------------------------|

| BIT                                                 | DESCRIPTION                    |

| 15 (MSB)                                            | ENHANCED INTERRUPTS            |

| 14                                                  | LOGIC "0"                      |

| 13                                                  | BUSY LOOKUP TABLE ENABLE       |

| 12                                                  | RX SA DOUBLE BUFFER ENABLE     |

| 11                                                  | OVERWRITE INVALID DATA         |

| 10                                                  | 256-WORD BOUNDARY DISABLE      |

| 9                                                   | TIME TAG RESOLUTION 2(TTR2)    |

| 8                                                   | TIME TAG RESOLUTION 1 (TTR1)   |

| 7                                                   | TIME TAG RESOLUTION 0 (TTR0)   |

| 6                                                   | CLEAR TIME TAG ON SYNCHRONIZE  |

| 5                                                   | LOAD TIME TAG ON SYNCHRONIZE   |

| 4                                                   | INTERRUPT STATUS AUTO CLEAR    |

| 3                                                   | LEVEL/PULSE* INTERRUPT REQUEST |

| 2                                                   | CLEAR SERVICE REQUEST          |

| 1                                                   | ENHANCED RT MEMORY MANAGEMENT  |

| 0 (LSB)                                             | SEPARATE BROADCAST DATA        |

| Т        | TABLE 7. START/RESET REGISTER (WRITE 06H) |  |

|----------|-------------------------------------------|--|

| BIT      | DESCRIPTION                               |  |

| 15 (MSB) | RESERVED                                  |  |

| •        | •                                         |  |

| •        | •                                         |  |

| •        | •                                         |  |

| 7        | RESERVED                                  |  |

| 6        | BC/MT STOP-ON-MESSAGE                     |  |

| 5        | BC STOP-ON-FRAME                          |  |

| 4        | TIME TAG TEST CLOCK                       |  |

| 3        | TIME TAG RESET                            |  |

| 2        | INTERRUPT RESET                           |  |

| 1        | BC/MT START                               |  |

| 0 (LSB)  | RESET                                     |  |

| TABLE 8. BC/RT COMMAND STACK POINTER REG. (READ 06H) |                          |

|------------------------------------------------------|--------------------------|

| BIT                                                  | DESCRIPTION              |

| 15 (MSB)                                             | COMMAND STACK POINTER 15 |

| •                                                    | •                        |

| •                                                    | •                        |

| •                                                    | •                        |

| 0 (LSB)                                              | COMMAND STACK POINTER 0  |

|          | TABLE 9. BC CONTROL WORD REGISTER<br>(READ/WRITE 08H) |  |

|----------|-------------------------------------------------------|--|

| BIT      | DESCRIPTION                                           |  |

| 15 (MSB) | RESERVED                                              |  |

| 14       | M.E. MASK                                             |  |

| 13       | SERVICE REQUEST BIT MASK                              |  |

| 12       | SUBSYS BUSY BIT MASK                                  |  |

| 11       | SUBSYS FLAG BIT MASK                                  |  |

| 10       | TERMINAL FLAG BIT MASK                                |  |

| 9        | RESERVED BITS MASK                                    |  |

| 8        | RETRY ENABLED                                         |  |

| 7        | BUS CHANNEL A/B                                       |  |

| 6        | OFF LINE SELF TEST                                    |  |

| 5        | MASK BROADCAST BIT                                    |  |

| 4        | EOM INTERRUPT ENABLE                                  |  |

| 3        | 1553A/B SELECT                                        |  |

| 2        | MODE CODE FORMAT                                      |  |

| 1        | BROADCAST FORMAT                                      |  |

| 0 (LSB)  | RT-RT FORMAT                                          |  |

| TABLE 10. RT SUBADDRESS CONTROL WORD REGISTER<br>(READ/WRITE 08H) |                                 |

|-------------------------------------------------------------------|---------------------------------|

| BIT                                                               | DESCRIPTION                     |

| 15 (MSB)                                                          | RX: DOUBLE BUFFER ENABLE        |

| 14                                                                | TX: EOM INT                     |

| 13                                                                | TX: CIRC BUF INT                |

| 12                                                                | TX: MEMORY MANAGEMENT 2 (MM2)   |

| 11                                                                | TX: MEMORY MANAGEMENT 1 (MM1)   |

| 10                                                                | TX: MEMORY MANAGEMENT 0 (MM0)   |

| 9                                                                 | RX: EOM INT                     |

| 8                                                                 | RX: CIRC BUF INT                |

| 7                                                                 | RX: MEMORY MANAGEMENT 2 (MM2)   |

| 6                                                                 | RX: MEMORY MANAGEMENT 1 (MM1)   |

| 5                                                                 | RX: MEMORY MANAGEMENT 0 (MM0)   |

| 4                                                                 | BCST: EOM INT                   |

| 3                                                                 | BCST: CIRC BUF INT              |

| 2                                                                 | BCST:MEMORY MANAGEMENT 2 (MM2)  |

| 1                                                                 | BCST: MEMORY MANAGEMENT 1 (MM1) |

| 0 (LSB)                                                           | BCST: MEMORY MANAGEMENT 0 (MM0) |

| TABLE 11. TIME TAG REGISTER (READ/WRITE 0AH) |             |

|----------------------------------------------|-------------|

| BIT                                          | DESCRIPTION |

| 15 (MSB)                                     | TIME TAG 15 |

| •                                            | •           |

| •                                            | •           |

| •                                            | •           |

| 0 (LSB)                                      | TIME TAG 0  |

| TABLE 1  | TABLE 12. INTERRUPT STATUS REGISTER (READ/WRITE 0CH) |  |

|----------|------------------------------------------------------|--|

| BIT      | DESCRIPTION                                          |  |

| 15 (MSB) | MASTER INTERRUPT                                     |  |

| 14       | RAM PARITY ERROR                                     |  |

| 13       | TRANSMITTER TIMEOUT                                  |  |

| 12       | BC/RT COMMAND STACK ROLLOVER                         |  |

| 11       | MT COMMAND STACK ROLLOVER                            |  |

| 10       | MT DATA STACK ROLLOVER                               |  |

| 9        | RT MODE/MT PATTERN TRIGGER                           |  |

| 8        | BC RETRY                                             |  |

| 7        | RT ADDRESS PARITY ERROR                              |  |

| 6        | TIME TAG ROLLOVER                                    |  |

| 5        | RT CIRCULAR BUFFER ROLLOVER                          |  |

| 4        | RT SUBADDRESS CONTROL WORD EOM                       |  |

| 3        | BC END OF FRAME                                      |  |

| 2        | FORMAT ERROR                                         |  |

| 1        | STATUS SET                                           |  |

| 0 (LSB)  | END OF MESSAGE                                       |  |

| TABLE 1  | TABLE 14. CONFIGURATION REGISTER #4 (READ/WRITE1 0H) |  |

|----------|------------------------------------------------------|--|

| BIT      | DESCRIPTION                                          |  |

| 15 (MSB) | EXTERNAL BIT WORD ENABLE                             |  |

| 14       | INHIBIT BIT WORD IF BUSY                             |  |

| 13       | MODE COMMAND OVERRIDE BUSY                           |  |

| 12       | EXPANDED BC CONTROL WORD ENABLE                      |  |

| 11       | BROADCAST MASK ENABLE/XOR                            |  |

| 10       | RETRY IF -A AND M.E.                                 |  |

| 9        | RETRY IF STATUS SET                                  |  |

| 8        | 1ST RETRY ALT/SAME BUS                               |  |

| 7        | 2ND RETRY ALT/SAME BUS                               |  |

| 6        | VALID M.E./NO DATA                                   |  |

| 5        | VALID BUSY/NO DATA                                   |  |

| 4        | MT TAG GAP OPTION                                    |  |

| 3        | LATCH RT ADDRESS WITH CONFIG #5                      |  |

| 2        | TEST MODE 2                                          |  |

| 1        | TEST MODE 1                                          |  |

| 0 (LSB)  | TEST MODE 0                                          |  |

| TABLE 13. CONFIGURATION REGISTER #3 (READ/WRITE 0EH) |                              |

|------------------------------------------------------|------------------------------|

| BIT                                                  | DESCRIPTION                  |

| 15 (MSB)                                             | ENHANCED MODE ENABLE         |

| 14                                                   | BC/RT COMMAND STACK SIZE 1   |

| 13                                                   | BC/RT COMMAND STACK SIZE 0   |

| 12                                                   | MT COMMAND STACK SIZE 1      |

| 11                                                   | MT COMMAND STACK SIZE 0      |

| 10                                                   | MT DATA STACk SIZE 2         |

| 9                                                    | MT DATA STACK SIZE 1         |

| 8                                                    | MT DATA STACk SIZE 0         |

| 7                                                    | ILLEGALIZATION DISABLED      |

| 6                                                    |                              |

| 5                                                    | ALTERNATE STATUS WORD ENABLE |

| 4                                                    | ILLEGAL RX TRANSFER DISABLE  |

| 3                                                    | BUSY RX TRANSFER DISABLE     |

| 2                                                    | RAFT-FLAG WRAP ENABLE        |

| 1                                                    | 1553A MODE CODES ENABLE      |

| 0 (LSB)                                              | ENHANCED MODE CODE HANDLING  |

| TABLE 15.       CONFIGURATION REGISTER #5 (READ/WRITE 12H) |                                                   |

|------------------------------------------------------------|---------------------------------------------------|

| BIT                                                        | DESCRIPTION                                       |

| 15 (MSB)                                                   | 12MHZ CLOCK SELECT                                |

| 14                                                         | LOGIC "0"                                         |

| 13                                                         | EXTERNAL TX INHIBIT A, read only BU-65170/61580X6 |

| 12                                                         | EXTERNAL TX INHIBIT B, read only BU-65170/61580X6 |

| 11                                                         | EXPANDED CROSSING ENABLED                         |

| 10                                                         | RESPONSE TIMEOUT SELECT 1                         |

| 9                                                          | RESPONSE TIMEOUT SELECT 0                         |

| 8                                                          | GAP CHECK ENABLED                                 |

| 7                                                          | BROADCAST DISABLED                                |

| 6                                                          | LOGIC "1"                                         |

| 5                                                          | RT ADDRESS 4                                      |

| 4                                                          | RT ADDRESS 3                                      |

| 3                                                          | RT ADDRESS 2                                      |

| 2                                                          | RT ADDRESS 1                                      |

| 1                                                          | RT ADDRESS 0                                      |

| 0 (LSB)                                                    | RT ADDRESS PARITY                                 |

| TABL     | TABLE 16. MONITOR DATA STACK ADDRESS REGISTER<br>(READ/WRITE 14H) |  |

|----------|-------------------------------------------------------------------|--|

| BIT      | DESCRIPTION                                                       |  |

| 15 (MSB) | MONITOR DATA STACK ADDRESS 15                                     |  |

| •        | •                                                                 |  |

| •        | •                                                                 |  |

| •        | •                                                                 |  |

| 0 (LSB)  | MONITOR DATA STACK ADDRESS 0                                      |  |

| TABLE 17. BC FRAME TIME REMAINING REGISTER<br>(READ/WRITE 16H) |                            |

|----------------------------------------------------------------|----------------------------|

| BIT                                                            | DESCRIPTION                |

| 15 (MSB)                                                       | BC FRAME TIME REMAINING 15 |

| •                                                              | •                          |

| •                                                              | •                          |

| •                                                              | •                          |

| 0 (LSB)                                                        | BC FRAME TIME REMAINING 0  |

| Note: resolution = 100 μs per LSB                              |                            |

| TABLE 20. RT STATUS REGISTER (READ 1CH) |                            |  |

|-----------------------------------------|----------------------------|--|

| BIT                                     | DESCRIPTION                |  |

| 15 (MSB)                                | RT ADDRESS 4               |  |

| 14                                      | RT ADDRESS 3               |  |

| 13                                      | RT ADDRESS 2               |  |

| 12                                      | RT ADDRESS 1               |  |

| 11                                      | RT ADDRESS 0               |  |

| 10                                      | MESSAGE ERROR              |  |

| 9                                       | INSTRUMENTATION            |  |

| 8                                       | SERVICE REQUEST            |  |

| 7                                       | RESERVED                   |  |

| 6                                       | RESERVED                   |  |

| 5                                       | RESERVED                   |  |

| 4                                       | BROADCAST COMMAND RECEIVED |  |

| 3                                       | BUSY                       |  |

| 2                                       | SUBSYSTEM FLAG             |  |

| 1                                       | DYNAMIC BUS CONTROL ACCEPT |  |

| 0 (LSB)                                 | TERMINAL FLAG              |  |

| TABLE 18. BC MESSAGE TIME REMAINING REGISTER<br>(READ 18H) |                              |  |

|------------------------------------------------------------|------------------------------|--|

| BIT                                                        | DESCRIPTION                  |  |

| 15 (MSB)                                                   | BC MESSAGE TIME REMAINING 15 |  |

| •                                                          | •                            |  |

| •                                                          | •                            |  |

| •                                                          | •                            |  |

| 0 (LSB)                                                    | BC MESSAGE TIME REMAINING 0  |  |

| Note: resolution = 1 μs per LSB                            |                              |  |

| TABLE 19. BC FRAME TIME/RT LAST COMMAND/MT TRIGGER<br>REGISTER (READ/WRITE 1AH) |             |  |

|---------------------------------------------------------------------------------|-------------|--|

| BIT                                                                             | DESCRIPTION |  |

| 15 (MSB)                                                                        | BIT 15      |  |

| •                                                                               | •           |  |

| •                                                                               | •           |  |

| •                                                                               | •           |  |

| 0 (LSB)                                                                         | BIT 0       |  |

| TABLE 21. RT BIT WORD REGISTER (READ 1EH) |                                  |  |

|-------------------------------------------|----------------------------------|--|

| BIT                                       | DESCRIPTION                      |  |

| 15 (MSB)                                  | TRANSMITTER TIMEOUT              |  |

| 14                                        | LOOP TEST FAILURE B              |  |

| 13                                        | LOOP TEST FAILURE A              |  |